原标题:摩尔定律的突围

编者按:本文来自半导体行业观察(ID:icbank),作者陈亮 ,创业邦经授权转载。封面图来自图虫创意。

50多年前,Intel创始人之一摩尔(Gordon Moore)提出了著名的摩尔定律,其内容为:集成电路上可容纳的晶体管数目,约每隔两年便会增加一倍;经常被引用的“18个月”,是由Intel首席执行官大卫·豪斯(David House)提出:预计18个月会将芯片的性能提高一倍,这是一种指数级的性能提升。摩尔定律并非自然规律,而应该被视为对未来集成电路发展的观测或者预测,但是这样的“预言”却伴随着集成电路半个多世纪的快速发展并不断的“自我实现”。

从实际使用角度看,摩尔定律可以理解为微处理器的性能每隔18个月提高一倍,或价格下降一半。集成电路集成度越高,晶体管的价格就越便宜,这也就自然的延伸出了摩尔定律的经济学意义,比如在20世纪60年代初,一个晶体管要10美元左右,但随着晶体管越来越小,小到一根头发丝上可以放1000个晶体管时,每个晶体管的价格只有千分之一美分,也即当初价格的百万分之一。

微处理器晶体管数量大幅上升

我们通过下面这个视频就可以一窥集成电路从1965年到2019年的发展史,同时也看到摩尔定律和集成电路相互“竞速飞奔“的55年。

视频中可以看出,摩尔定律贯穿着从早期的IBM 用集成电路设计出电脑计算单元,到以Intel为代表的IDM半导体公司成立,再到以联华电子和台积电为代表的Foundry厂商崛起,最终至目前以台积电为代表的晶圆制造作为核心的全产业链服务平台的建立,其不断实现的过程也是产业链持续进化的结果。

一、摩尔定律“死”了么?

随着新工艺节点的不断推出,晶体管体积越来越小,种种物理极限制约着其进一步发展。比如当晶体管沟道区域长度足够短的时候,量子穿隧效应就会发生,会导致漏电流增加,进而导致晶体管效能的下降。

摩尔定律是否已“死”?业内大咖有着不同的观点。以Nvidia CEO黄仁勋为代表的一方认为摩尔定律已“死”,而以前AMD 首席架构师Jim Keller和台积电为代表的一方认为摩尔定律依然可以指引领集成电路行业发展,其实综合两方观点看,表面相反的观点但本质却并不矛盾,黄仁勋认为半导体物理学的限制意味着如今CPU性能每年只能提升20%左右,摩尔定律已走向终结;而Jim Keller和台积电则认为摩尔定律并非简单的描述单位面积晶圆上晶体管数量的变化趋势,而是从高性能计算目标的实现角度讲,依然有很多方法可以让集成电路在面积可控的前提下实现计算性能的指数级增长,从而实现我们经常说到的高性能芯片设计和制造的PPA目标(High Performance,Low Power,Area Denser)。那么在摩尔定律进入深水区以后,半导体的发展方向是什么呢?

二、More than Moore’s Law的四种方向?

结合目前高性能计算芯片发展趋势来讲,通过等比例缩放晶体管长度的二维化模式来延展摩尔定律已经变得越来越难,我们需要从第一性原理出发来理解摩尔定律背后所反映的芯片发展规律,即芯片技术的持续进步是人类生产力不断发展的缩影,摩尔定律是关于芯片技术进步的一种定量化的具体表现形式,我们将其目标简单抽象概括为“单位面积芯片在每瓦每单位成本的基础上实现更高计算能力”。虽然在先进制程进入到5nm以后,摩尔定律的实现已经有所放缓,但微观层面芯片设计依旧将持续朝着更高的计算密度,更大的存储密度和更紧的连接密度三个方向持续推进,同时行业新的理念和技术方法仍将为摩尔定律注入新的血液,比如采用非经典结构,从结构的设计及布局来实现芯片面积的微缩,从而促使摩尔定律在“另类”层面得以实现。下面就摩尔定律未来的演进方式简单展开:

1、晶体管结构由平面型向3D立体化演进

晶体管由Planar FET(平面场效应晶体管)向FinFET (鳍式场效应晶体管)发展,再到最新的以nanosheet FET(堆叠纳米片场效应晶体管)和nanowire(纳米线)为代表的GAA(Gate all around)的新一代晶体管结构, 本质上都是要解决芯片上晶体管中电荷泄漏到栅极附近导致开关效率不高的问题,从而提高运算性能并降低功耗。

2、由强调晶体管密度向强调功能密度过渡

所谓功能密度是指单位体积内包含的功能单位的数量,而功能单位是指能够完成一定功能的逻辑单元,如ALU(算术逻辑单元),I/O Control Unit(输入输出控制单元),CPU(中央处理单元),Memory(存储器)等,所以无论是多核设计,片上存储或者高密度的线宽,还是异构计算的加速器,本质上是提升芯片的功能密度,晶体管密度不再是摩尔定律参考的唯一指标。

3、二维化扩展向异构集成过渡

芯片将由传统的平面型制造和封装技术向2.5D、3D等先进制造和封装技术过渡,可将不同尺寸、制程工艺及材料的芯片组合,通过chip to chip或者die to die互联技术制造出比单片芯片更灵活的可扩展芯片组,同时具有低功耗和高性能的特点。

4、由硬件发展向软硬件一体化方式过渡

芯片计算性能的提升已经不止依靠简单的增加核数或者主频来实现,而是通过微架构的设计,异构计算的整合和专业的并行计算平台部署来实现,无论是Intel、Nivdia、AMD或者Xilinx都在各自的应用领域构筑了“云+端”的一体化计算能力壁垒。

当前最能代表摩尔定律的技术方向是高性能计算芯片,但性能的提升却逐渐从设计端向制造和封测端倾斜,我们通过对以上四点进行展开,来了解未来摩尔定律的延伸方向。

三、摩尔定律突围的四种方式

1、晶体管结构和材料创新最摩尔定律直接的“续命”方式

1)Dennard Scaling 指导第一阶

我们把摩尔定律的演进分为三个阶段,第一阶段是Dennard Scaling阶段,这是摩尔定律下的一个细分理论,主要内容是晶体管的尺寸在每一代技术中都缩小了30% (0.7倍) ,这意味着电路减少了30% (0.7倍)的延迟,因此增加了约40% (1.4倍)的工作频率,同时为了保持电场恒定,电压降低了30% (电场强度=电压/两点场强距离,距离和工作频率成反比),功耗降低了50% (与电压平方成正比)。因此,在每一代技术中,晶体管密度增加一倍,电路速度提高40%,功耗可以保持不变。

工艺制程推动摩尔定律不断实现

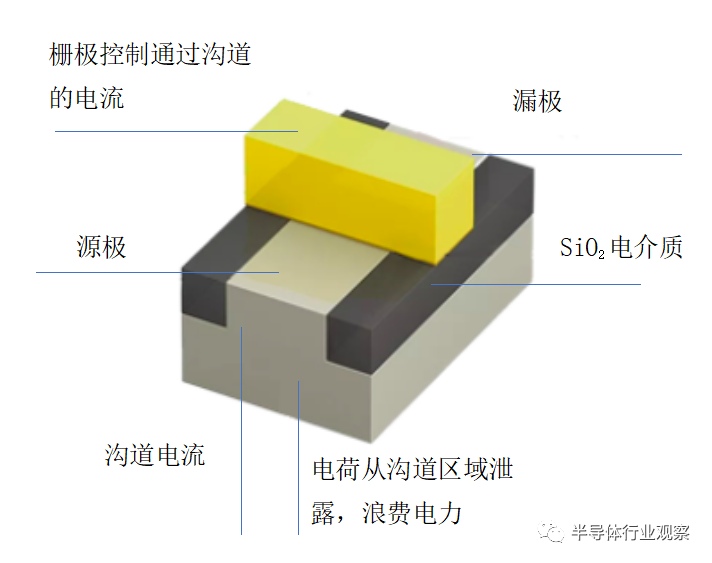

在最初的3um到0.13um制程的提升过程中,Dennard Scaling都是有效的,但是0.13um以后Dennard Scaling便逐渐失效,主要原因是在芯片尺寸不变,晶体管变小,数量变多的情况下,沟道区域电流泄漏会导致晶体管升温,从而导致芯片的功耗上升,打破了晶体管数量,计算速率和能耗之间简单的线性递推关系。反映到现状,就是CPU厂商不再能简单的依靠增加时钟频率和核数来提高计算能力,因为整体功耗的大幅增加只会使一部分核处于理想的工作状态。

2)新材料突破第二阶段

为了防止晶体管沟道区域的电流泄露,需要缩小栅极和沟道区域的二氧化硅氧化层,用来增大栅极和沟道区域之间的电容。但在0.13um至28nm制程阶段,氧化层已经不能再缩小了,电压的影响也越来越大,这时候需要找到高介电常数(high-k)的物质,来增加电容,从而获得低沟道漏电的效果,降低能量损耗。

中芯国际在2016年通过HKMG技术(添加high-k材料)实现了28nm制程良率大幅提升,而其14nm制程则采用了FinFET技术,相对于HKMG则是工艺上进一步的提升。

除了添加high-k材料外,碳纳米管作为全新的低温材料,因具有较高的电子和空穴迁移率、稳定的结构和散热性能,是构建高性能晶体管的理想沟道材料,使用碳纳米管材料取代硅时,甚至不需要采用类似于FinFET的晶体管堆叠技术,依然可以取得良好的效能。

3)晶体管结构创新

在制程大于28nm的时候,Planar (平面型)结构的晶体管是可以满足Dennard Scaling的,集成电路依然可以依靠晶体管长度实现功能的线性扩展。

平面型半导体晶体管结构

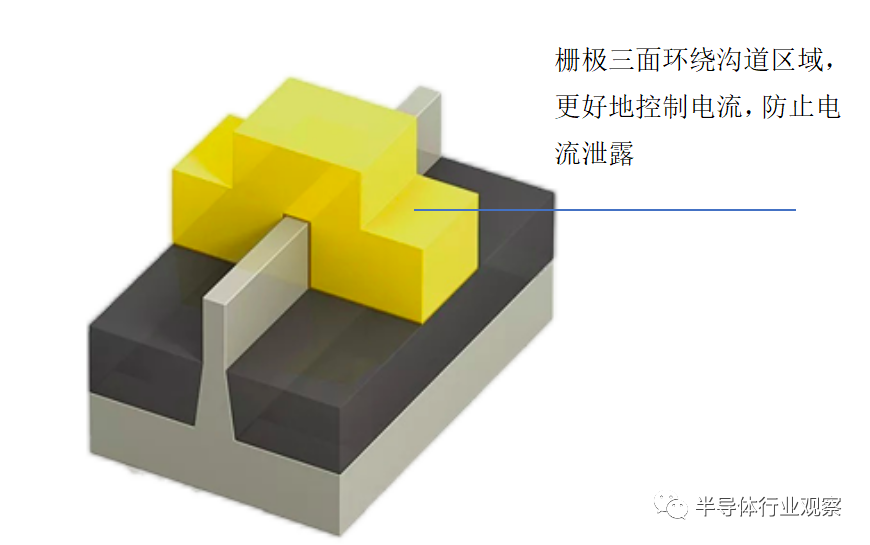

当制程小于28nm时候,SiO2介质会变得越来越薄,导致漏电电流越来越大,HKMG技术已经不能提高芯片良率和热稳定性,这时候需要胡正明教授提出的FinFET结构晶体管才可以有效提升制程工艺稳定性。

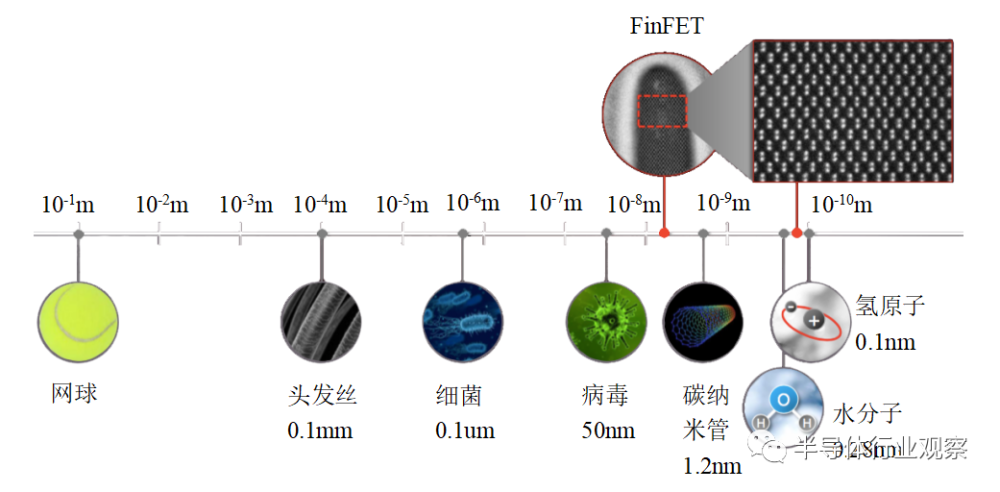

FinFET晶体管大小介于病毒和碳纳米管之间

2019年12月,国际电子电气工程学会(IEEE)公布了2020年IEEE荣誉奖章获得者,华人学者胡正明获奖,他是历史上第三位获得该奖项的华人学者,前两位获得者分别是前贝尔实验室主任卓以和以及台积电创始人张忠谋。胡正明获奖原因是他“开发半导体模型并将其投入生产实践,尤其是3D器件结构,使摩尔定律又持续了数十年”。这项发明被看做是50多年来半导体技术的重大突破。胡正明于1999年先后提出了FD-SOI和FinFET技术,因此被称为3D晶体管之父。

FinFET晶体管结构

FinFET的的结构中,栅极三面包围了整个沟道,相比于Planar结构,增加了对沟道的控制面积,也意味着漏电电流可以进一步降低。而FD-SOI本质上还是一种平面工艺,其关键点是在硅上添加一层很薄的氧化物薄膜层,更好的增强晶体管的静电特性,但尺寸和厚度难以缩小,在到达12nm制程之后,效果将会大大减弱,目前来看,三星和Global Foundry在22nm-14nm制程环节采用FD-SOI技术,10nm-5nm阶段采用FinFET技术,而台积电始终采用FinFET技术。

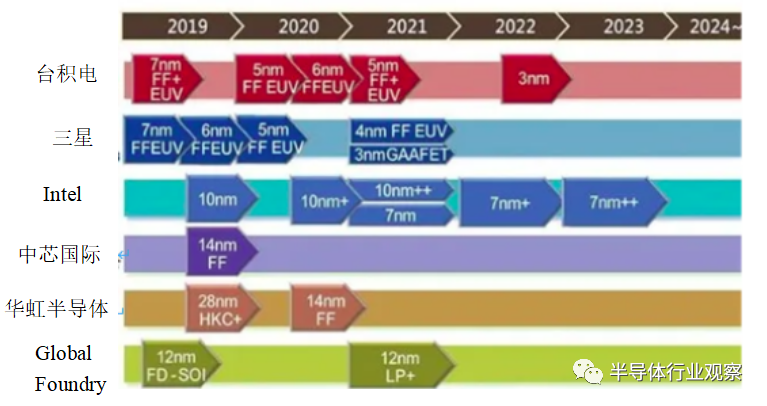

在Global Foundry和联电宣布放弃10nm以内先进制程追赶以后,目前只有台积电、三星、Intel和中芯国际四家厂商还在继续打造半导体更先进的制程,其中台积电和三星则在2020年可以实现5nm制程量产,但Intel还停留在追求10nm制程阶段,这导致Intel最新的Lakefield CPU可能依然采用自家的10nm工艺,但是对于加速性能要求更高的GPU,Intel即将推出的Xe Graphics系列独显产品将可能采用台积电的5nm制程,同7nm制程的Nvidia Ampere 和AMD RDNA 2竞争。

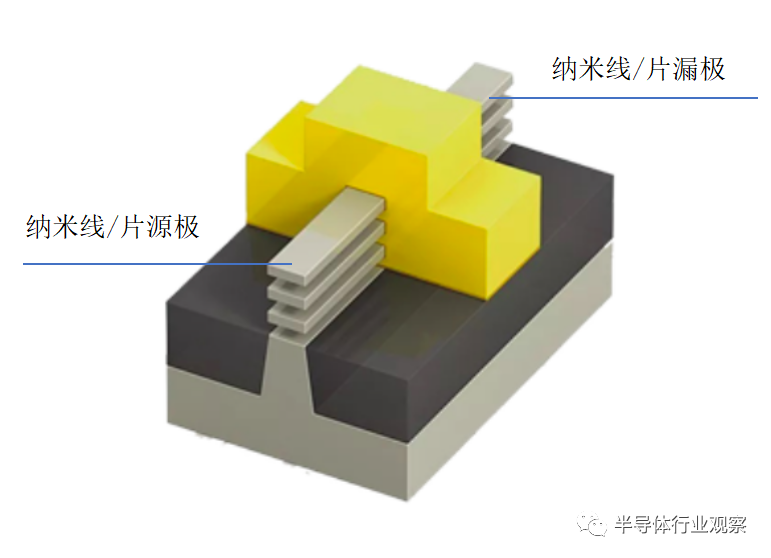

在3nm制程以后,两家半导体制造巨头台积电和三星的技术路径便 “分道扬镳”,台积电依然坚持FinFET 技术,而三星选择更新的GAA技术(Gate-all-around),所谓GAA,是指全环栅晶体管,是一种继续延续现有半导体技术路线寿命的较主流方案,可进一步增强栅极控制电流能力,使得底部与硅体完全隔离,因而泄漏电流即便在晶体管关闭时也不会流动,能克服当前技术的物理缩放比例和性能限制。

GAA晶体管结构

GAA结构不但要使用新型的晶体管结构,还要借助新的材料工艺,那就是纳米线或纳米片。纳米线/片一头作为源极,一头作为栅极,同时被栅极包围,电流沿着纳米线/片沟道传输,但因为纳米线太细,导致沟道电流传输效率和开关关断效率较低,因此考虑宽度更大的纳米板,可以获得更多沟道宽度以及电流,当宽度太大时,也可以考虑缩窄来降低功耗,这样就具备了调整晶体管能效的灵活性,但是目前GAA工艺依然处于研发阶段,具体效果只有等三星3nm风险试产以后才能看到。

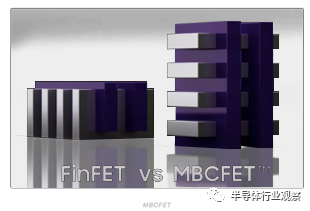

同时,三星也提出了更加激进的晶体管结构工艺,即MBCFET(Multi bridge Channle FET)的结构,类似于将多个FinFET的结构再进行堆叠。晶体管纵向排列的好处显而易见,提高了单位面积的晶体管数量,但结构的复杂性也让晶体管的功耗成为一个问题,限制了堆叠技术的发展,未来提升效能的方向可能是我们上文提到的晶体管堆叠+碳纳米管新材料相结合的方式。

三星提出MBCFET技术

2、异构体系是延伸摩尔定律的有效途径

当代社会快速发展下,HPC和AI对算力要求越来越高,在这样的背景下,传统的以冯·诺依曼为代表的通用计算架构已经不能满足芯片发展需求,尖端计算芯片的发展将从通用计算架构向异构计算架构转移,而异构计算架构主要有以下几个特点:一是它由许多功能单元组成,异构计算架构通常有多个DIE,每个DIE专用于执行一种功能,比如存储,计算和传输等。第二,是它打破了通用计算架构的“内存墙”,对计算和存储的物理位置和访问协议进行优化;第三,一般是在通用计算架构上创新设计或采用独特的ASIC架构;第四,有时会用到新的编程语言和指令集。下面我们从对Chiplet和EMIB新型架构设计以及Cerebras和Groq加速器设计介绍来简单展开。

1)AMD的Chiplet

说起芯片异构计算,让笔者最早想到的是ARM提到的big.little架构理念,即异构核心理念,即让处理器同时包括有低处理能力、低功耗的核心和高处理能力,高功耗的核心,同时共享缓存,根据不同的运算需求调度不同的运算资源,这样就能最大程度的平衡PPA,避免依靠单纯提高时钟速率(clock speed scaling)导致的暗硅效应(dark silicon)。我们经常看到的手机AP配置便是如此,比如市场传言AMD可能要做的手机AP配置核心就包括两颗Cortex-X1(频率3GHz)+两颗Cortex-A78(频率2.6GHz)+4 颗Cortex-A55(频率2GHz),这是一个考虑性能和功耗的均衡配置。

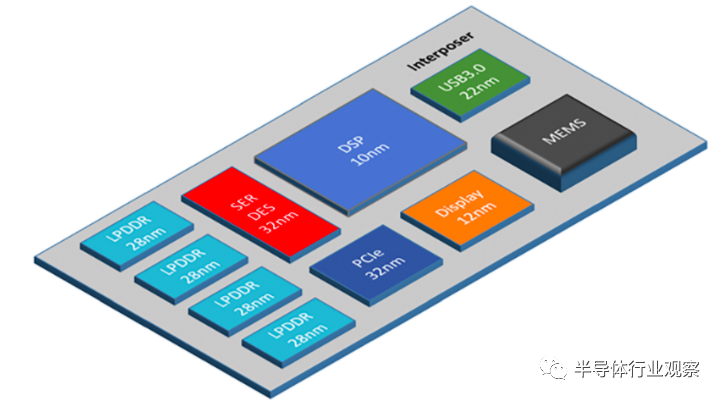

如果从ARM的架构理念延展开来,就不得不提最近AMD和Intel等大厂在力推的Chiplet技术,Chiplet是指一个芯片网络,通过将芯片设计中各复杂功能进行分解,然后开发出多种具有单一特定功能、可相互进行连接的裸芯片,实现数据存储、计算、信号处理、信号传输等功能,并最终以此为基础,建立一个die-to-die芯片网络,达到PPA的平衡。

Chiplet示意图

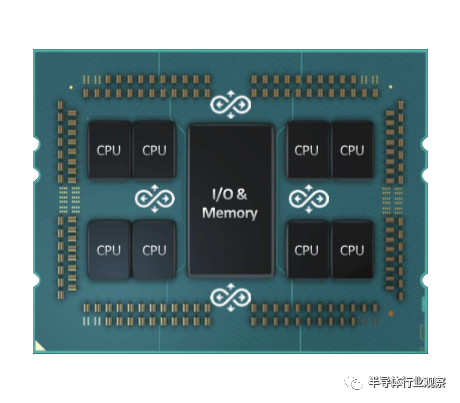

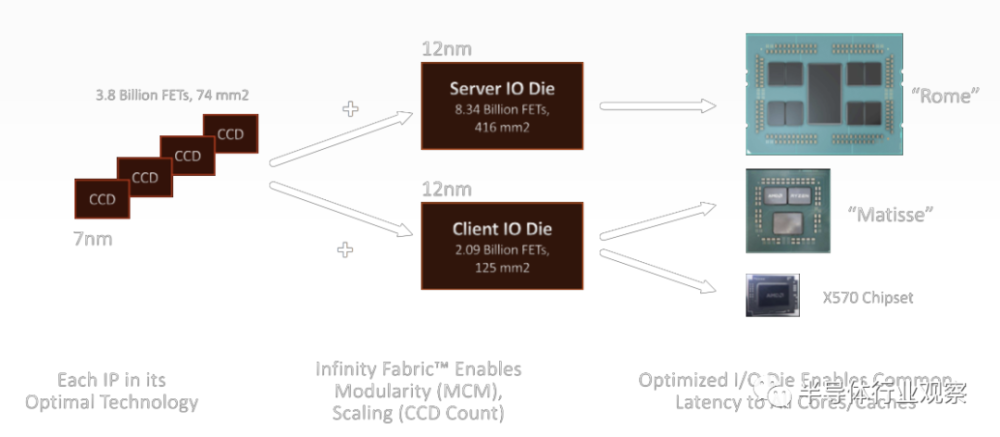

Chiplet示意图AMD第二代EPYC服务器处理器ROME采用Chiplet设计,将台积电先进制程7nm工艺制造的CPU模块与Global Foundry成熟制程12/14nm工艺制造的I/O模块组合,7nm可满足高算力的需求,12/14nm则降低了制造成本。这带来的好处是,7nm制程部分的芯片面积大幅缩减,而采用更成熟制程的I/O模块有助于整体良率的提升,进一步降低晶圆代工成本。

EPYC Chiplet设计

如上图所示,我们可以看到Chiplet 上IOD模块在中间位置,里面包含内存控制器和PCIe通道 ,两侧各有1个CCX模块(每个CCX包含4个CPU核),AMD开发了他们之间互联的接口协议Infinity Fabric,IOD 采用14nm 工艺,CCX中采用7nm工艺。

Chiplet让处理器设计更便捷

上图中CCD其实是Core Chiplet Die的缩写,是伴随最新的Zen 2架构处理器所诞生的缩写,标准化的CCD设计搭配服务器的IOD模块和PC机的IOD模块,分别可以组成服务器芯片Rome和PC芯片Zen 2。

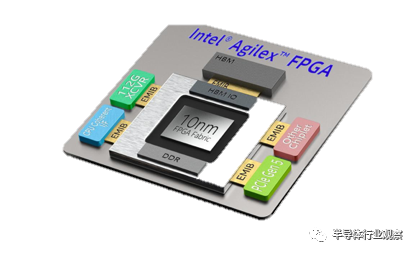

2)Intel的EMIB

Intel所推进的EMIB技术和AMD强调的Chiplet大体上思路是一致的,Intel使用EMIB技术的代表产品是FPGU Agilex,Agilex的中心是FPGA的核心逻辑LUT(查找表),采用10nm打造,同时EMIB技术将LUT与Xeon处理器、SerDes收发器、PCIe Gen 5、 DDR5、HBM2和Optane持久内存的进行整合,打造了一个高级的异构封装系统,其可被用于5G基站和打造数据分析的高级解决方案。

Intel EMIB技术

Agilex片上连接使用的是Intel开发的AIB总线技术(AMD对应的是 Infinity Fabric),Intel 没有兼容 Infinity Fabric和Nvidia的Nvlink和NvSwitch总线技术,虽然三家都强调模块化设计,但是依然是“各自为政”的状态,片内通信接口的不兼容导致芯片设计和融合不方便,不利于各家厂商嫁接其他厂商的产品功能,不利于打造开放的计算平台,各家依然筑起了各自的生态壁垒。尽管有DAPRA (美国国防部高级研究计划局)和OCP ODSA(开放计算项目)等项目在着力推进小芯片接口标准化,但独立第三方小芯片供应的商业模式何时能在芯片产业中普及,尚未可知。

3)Cerebras的超大芯片

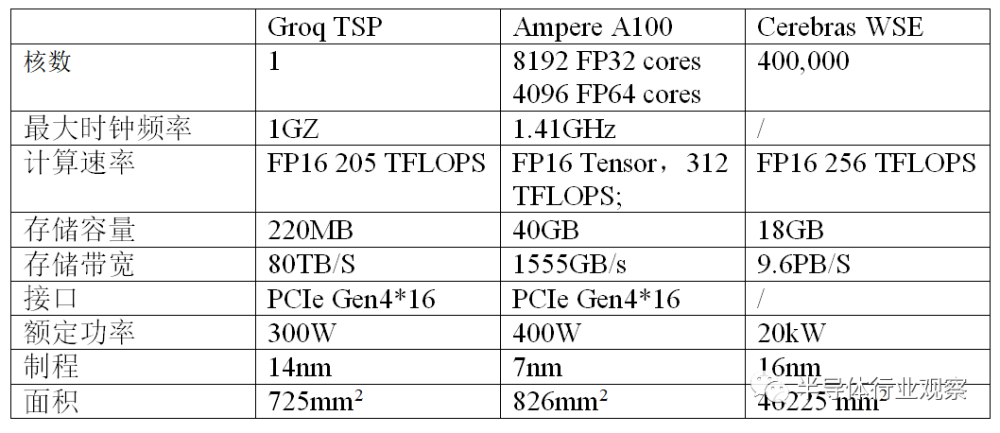

不同于传统的芯片架构设计模式,Cerebras设计的晶圆级引擎(Wafer Scale Engine,WSE)芯片“简单粗暴”, 一整个大片晶圆可以容纳1.2万亿个晶体管,面积为46,225平方毫米,晶体管密度为0.26亿/平方毫米,而Nvidia最新Ampere架构826平方毫米可以容纳542亿个晶体管,晶体管密度为0.66亿/平方毫米。

Cerebras和Nivida Ampere对比

其实Cerebras是通过突破晶圆尺寸限制,以“剑走偏锋”的大尺寸芯片设计提升计算和通信效率,降低“内存墙”的影响,让所有的内核都配有自己的片上内存,内核和存储以及内核和内核之前的通信效率大大提升,远高于Infinity Fabric这样的片内通信技术和InfiniBand等片外技术,这样就实现了我们前文所说的更高的晶体管密度(专为深度学习打造),更大的存储密度(贴近核的片上存储)和更紧的连接密度(高宽度,低延迟),达到了类似于小集群的计算能力,却不需要建设小集群。

但Cerebras也是有一些难点需要克服,比如芯片的制造和封测难度比较大,尤其是封测需要将PCB、Substrate(基板)和Interposer(内插板)和芯片等堆叠,对尺寸、精度和功耗都有较高要求,需要有专业的高技术封测厂商才能完成。且根据玻色-爱因斯坦(BOSE-EINSTEIN)良率模型, Y = 1 /(1 + AD)^ k(Y为良率,A为芯片面积,D为缺陷密度,k为难度系数),芯片面积越大,良率越低,这也是Cerebras能否实现商业化需要解决的问题。

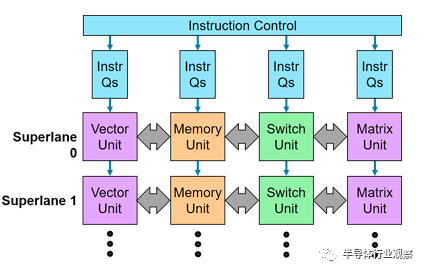

4)Groq的SDH(软件定义硬件)

Groq是由谷歌TPU前工程师团队打造的专注于云端AI推理的高性能芯片,他们强调的核心理念是“软件定义硬件”,即以单一核配置计算和存储单元的形式来代替传统的GPU多核模式,同时所有的操作都是通过软件预先设定。

Groq结构图

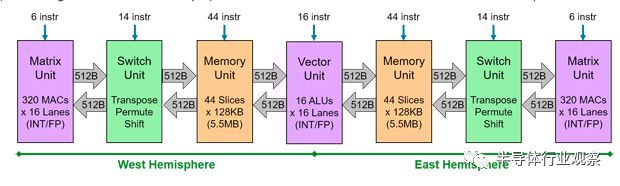

Groq结构图Groq的TSP(Tensor Stream Processor)的基本架构如上图。它的每一个指令执行组Superlane包括Vector Unit,Memory Unit,Switch Unit和Matrix Unit,其中Vector Unit主要做一些简单的算术逻辑运算,Memory Unit则是存储单元,Switch Unit主要承担张量数据的转换和不同Superlane的信息沟通,Matrix Unit承担主要的复杂运算。数据在Superlane中沿“东西”方向双向流动。每个执行的指令来自指令队列,所有的指令形成一个类似VLIW(超长指令架构的144路指令),按从“北”到“南”的方向以脉动的形式传递。也就是一个Superlane里的指令执行完之后,一条144路VLIW指令向下一个Superlane传递并执行,一共20条Superlane。这样的处理方式类似于我们所说的FPGA的工作方式,对于低延迟的流式数据处理效果很好,因此在batch size比较小的时候,推理的效果是要比GPU这种擅长处理大批量同构数据的更好。

从这里我们也可以思考,通用加速器对于硬件创业公司难度很大,而且在Nvidia拥有GPU+CUDA生态壁垒的情况下很难突围,不如先做好软件应用,然后top to bottom,做好针对性的加速硬件。

各功能单元之间有16通道

Groq并非采用传统的“冯诺依曼”指数集架构,而是采用了数据流架构,简化了硬件设计,不再有单独的指令控制功能,而是通过数据流动次序,而不是指令执行次序保证计算执行顺序,以压缩计算资源的每一个空闲时钟来提高计算效率,但与此同时,编译功能的负担却加重了,需要同时安排好144路纵向指令和横向320 byte数据流,而因为缺少寄存器之类的硬件,编译器必须确保流数据在指定的时间可供函数单元执行指定的指令。

不同芯片配置

可以看出,Groq、Nvidia A100和Cerebras在产品设计方面都做了差异化的设计,以更好地平衡PPA目标。

异构计算快速发展的同时也出现了一定的隐忧,主要是因为各家厂商在高速互联技术方面并不兼容和匹配,Intel不支持Nivdia的NvLink和NvSwitch,而AMD、ARM、Nvidia和Xilinx等公司先后搞出了CCIX、PCIe Gen-Z和OpenCAPI等开放内存互联协议,巧的是,这三大开放互联内存协议都将Intel排除在外,而Intel自己搞了CXL加速协议,在异构计算这块,高速互联技术协议的不统一,让各家公司产品实现兼容变得困难。

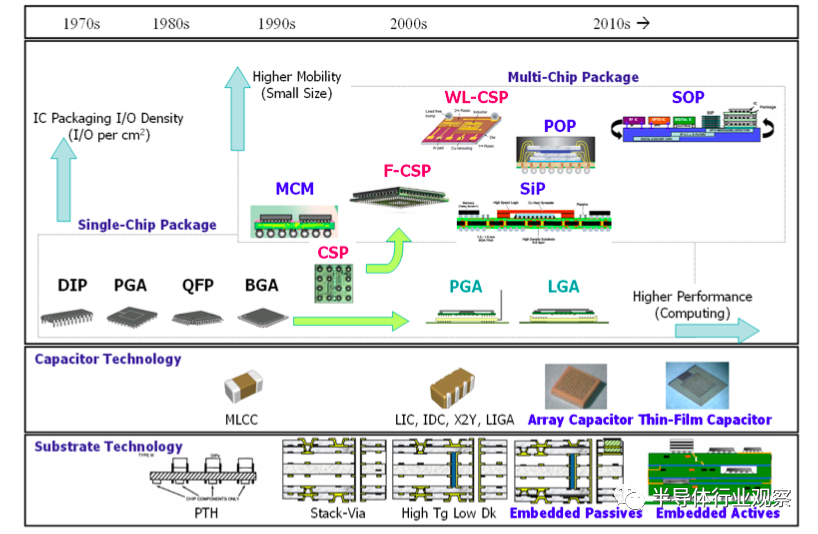

3、芯片封装将成为延续摩尔定律的重要一环

芯片封装测试在传统的印象里一般有着“人力密集”、“技术含量较低”和“利润率较低”的标签,但随着摩尔定律走进“深水区”以及芯片设计和制造愈发复杂以后,先进封装技术的重要性也越来越凸显。我们知道世界知名的封装厂除了ASE(日月光)、Ankor(安靠)以及长电科技这类OSAT厂以外,还有台积电和三星这类芯片制造和封装一体化的公司,因为中低端封装属于价值曲线的底部,遵循成本领先的战略,而高端封装主要面向手机SOC, HPC芯片和AI芯片等业务,需要和制造工艺紧密结合,所以地理位置上贴近客户端和制造端成为封装厂的核心优势之一,从这一点上讲,未来制造和封测一体化的趋势将会越来越明显,在高性能芯片方面,台积电和三星这类公司比OSAT公司更有优势。

回到摩尔定律的话题,高端封装技术从中观的系统角度出发更有针对性的提升芯片的功能密度,即通过将系统芯片高度集成到一个模块内,我们称之为系统级封装,用来实现我们前文所说的更高的晶体管密度,更大的存储密度和更紧的连接密度,系统级封装模块的体积决定着相同面积上的芯片可以集成器件数量,合理的模块设计体现出集成性(integration)、连接性(interconnection)和智能化(intelligence)的三个方面的平衡。

2.5D或者3D封装技术便体现出系统级封装的工艺水平,把不同功能的芯片或结构,通过堆叠技术或过孔互连等微机械加工技术,使其在垂直方向上形成立体集成和信号连通的技术。因为在垂直方向上有了功能和信号的延伸,所以有芯片堆叠的一般都可以称之为2.5D或者3D(区分后面讲到)。3D封装运用到的技术有封装堆叠(PoP)和硅通孔技术(TSV)等。

系统级封装技术的重要性可以从当年台积电利用其先进的Fanout PoP堆叠封装技术,击败三星从而独享整个苹果A12的制造和封测订单看出,之后无论是海思采用的FCCSP PoP技术海思高通采用的MceP PoP可以说都是3D封装技术的不同表现形式,可见高性能芯片生产越来越依靠厂商先进制程和先进封装的综合能力。

我们一一对平面封装、2.5D封装和3D封装进行结构展示:

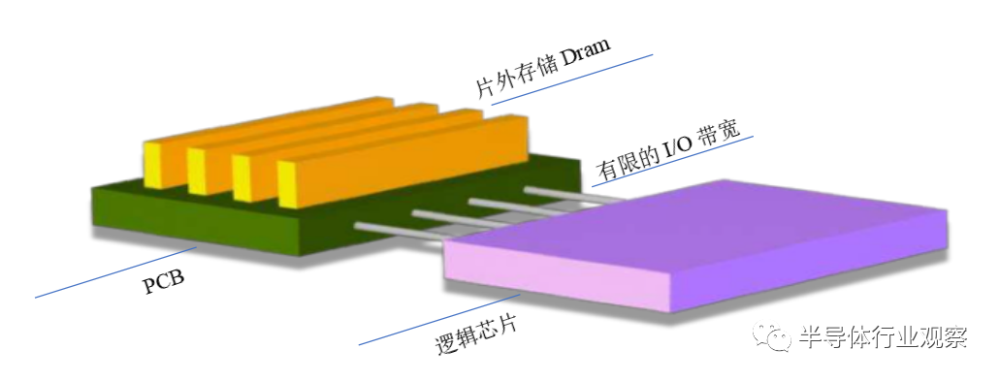

传统平面封装

平面封装带宽宽度有限,数据传输延迟较高,占用空间大,能耗水平也相对较高。

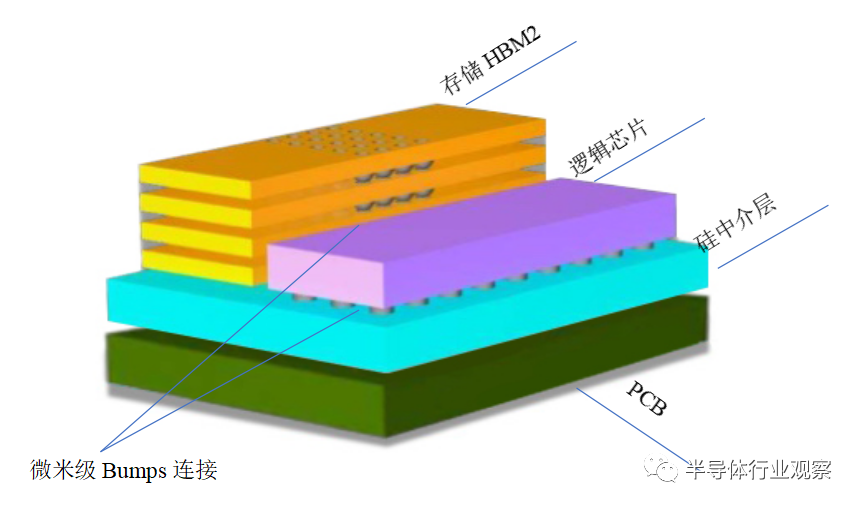

过渡性质的2.5D封装

2.5D封装是一种过渡的形式,目前Intel FPGA Agilex采用的EMIB封装形式就是2.5D封装,不过后续Intel 预计会对Xe Graphics GPU等新产品采用Foveros 3D封装形式。

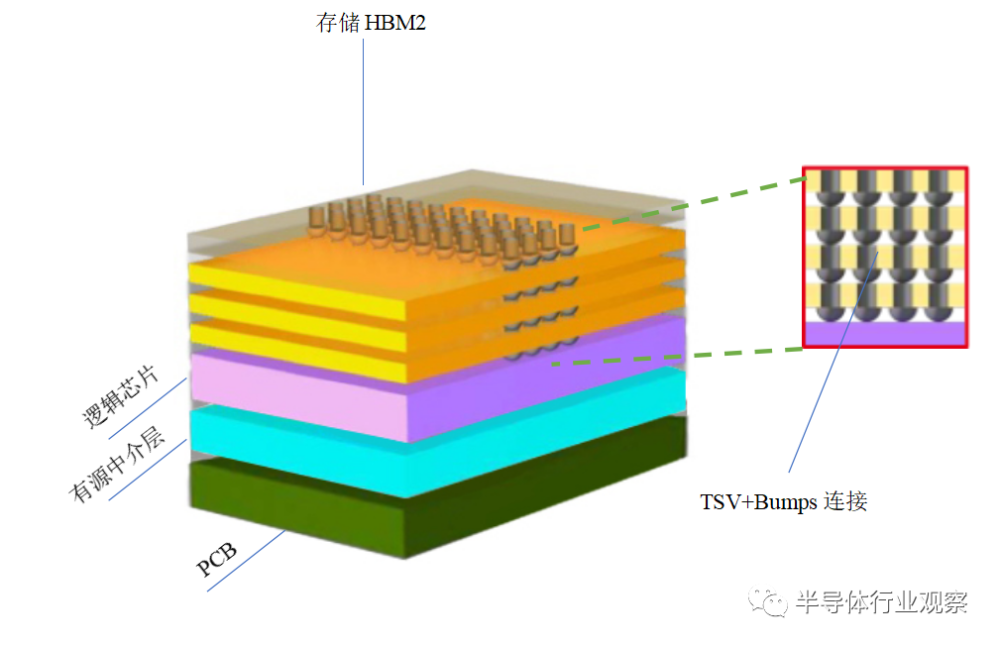

3D封装

3D封装通过TSV(through silicon via)技术将高速存储HBM2和逻辑芯片连接起来,有效缩短互连线长度,减少信号传输延迟和损失,提高信号传输速度和带宽,降低功耗和封装体积,实现多功能、高性能、高可靠性且更轻、更薄、更小的芯片系统级封装。其中硅中介层(interposer)对于TSV技术至关重要,一般硅中介层会布置由晶圆厂制造的有源电路,主要的I/O接口(如DDR或HBM2)电路将会在这块有源硅载片上实现,因为I/O电路并不需要10nm这样的尖端工艺,使用22nm或14nm无论是对于成本、良率还是混合电路设计难度来说都是最适合的。这样有源中介层集成了开关电容器稳压电路、逻辑芯片、灵活的分布式互联和片上存储器各个部分,并将它们连接在一起,可提供节能的多核计算架构。

系统级封装的进展历程

系统级封装逐渐提升封装密度,降低功能单元体积和面积大小的同时提高I/O连接数,更好地实现PPA目标。

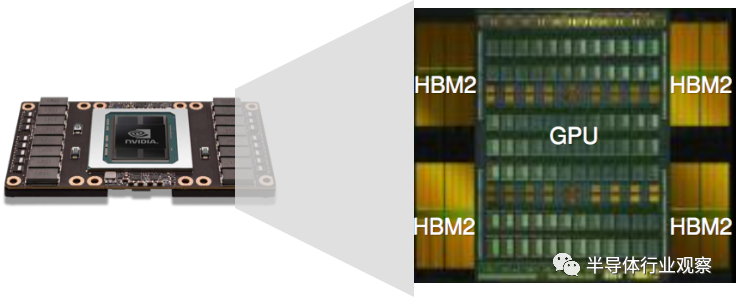

我们先从拥有最先进封装技术的台积电讲起,台积电将其封装技术称为晶圆级系统集成(Wafer Level System Integration),是其最主要的四个核心业务之一,Nivdia最新的Ampere架构GPU A100就是采用台积电7nm制程+CoWoS封装技术(Chip on Wafer on Substrate)

Nvidia的Ampere采用CoWoS封装技术

GPU A100由542亿个晶体管组成,采用的CoWoS技术将HBM2存储器安置在与GPU芯片相同的有源中介层和基板上,I/O连接密度大幅提升,可以提供近1.6TB/s的存储带宽,大幅超过V100系列的900GB/s带宽。

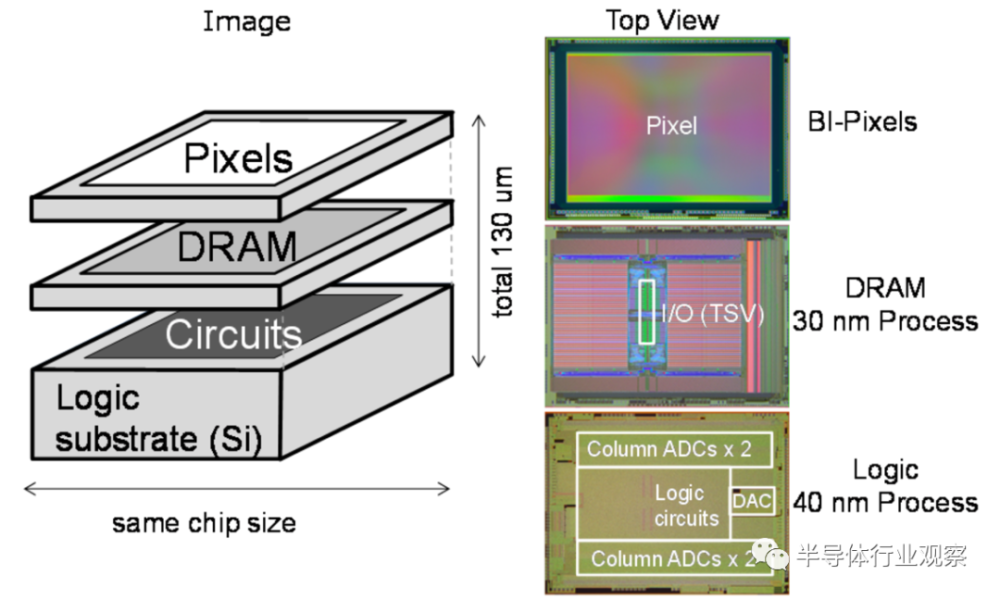

除了提到的A100系列,海思和Xilinx也曾使用过台积电的CoWos技术进行芯片封装,而除了高性能计算芯片以外,索尼也曾设计过3层堆叠的CMOS芯片,大大提高了像素的传输速率和处理性能。

索尼三层堆叠背照式CMOS

索尼的3D像素堆叠技术将CMOS的像素层和逻辑层进行了分离和堆叠,并在他们之间添加一层Dram,上下之间通过TSV技术进行连接,这样做可以提升CMOS芯片的面积占比,同时也能缩小其尺寸,而Dram的存在使得它可以在芯片上以超过24fps帧率的速度缓存180张以上原始的2000万像素图像,而且模数转换后的数据不会再因为MIPI-CSI总线传输能力有限而阻塞,这些数据可以被处理成一个文件并传输进内存芯片,然后再统一进行传输。

如果我们考虑在逻辑层添加AI处理器,则可以将图片信息在边缘侧进行处理或者机器学习,相比于分立式的AI处理器数据传输效率更高,功耗更低,能够广泛应用于AIOT、工业和安防等领域。

4、通信技术是摩尔硬件魔法的重要补充

摩尔定律是作为硬件的芯片自我实现的一条路径,但单依靠硬件已经无法满足下游服务器和高性能计算的与日俱增的需求,摩尔定律的延伸需要通过通信技术或者软件来实现。

2020年4月,Nvidia击败Intel,支付超过70亿美元成功收购了Mellanox和Cumulus Network,分别从智能网络芯片、高速互联技术和网络系统管理软件两方面入手,以软硬件相结合的方式对数据中心的通信进行优化和加速,大大提升了其在高性能计算领域的话语权,可以说,Nvidia已不再是一个单纯的GPU公司。

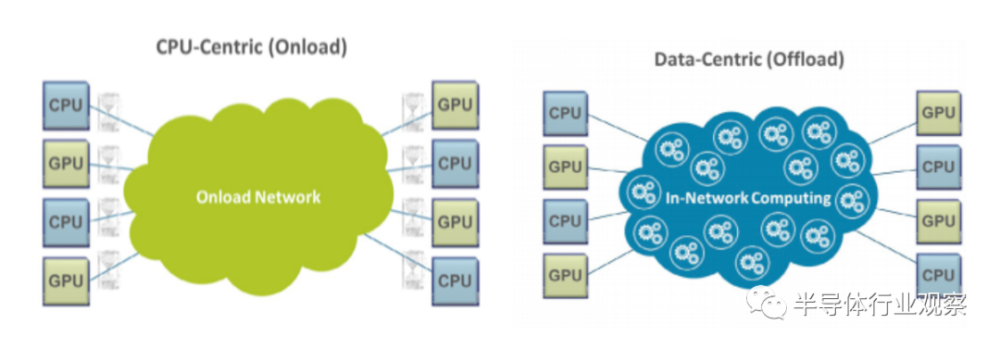

我们知道,以太网连接加速器最早可以追溯到微软2015年就开始在其云计算服务Azure中布局的Project Catapult,这是通过以太网连接的FPGA在数据中心对服务进行加速的方案。该方案在每台服务器的CPU和NIC(网卡)之间放置一个有自己协议栈的FPGA,FPGA利用服务器之间的以太网进行互联通信,而FPGA的本质是对CPU处理网络通信的功能进行卸载(offload),由FPGA来专门处理服务器之间的通信,这样可以让CPU专注于计算。Mellanox和Cumulus大大增强了Nvidia在数据中心的计算能力,而计算能力的提高,并非通过芯片升级来实现,而是通过网络加速来实现。

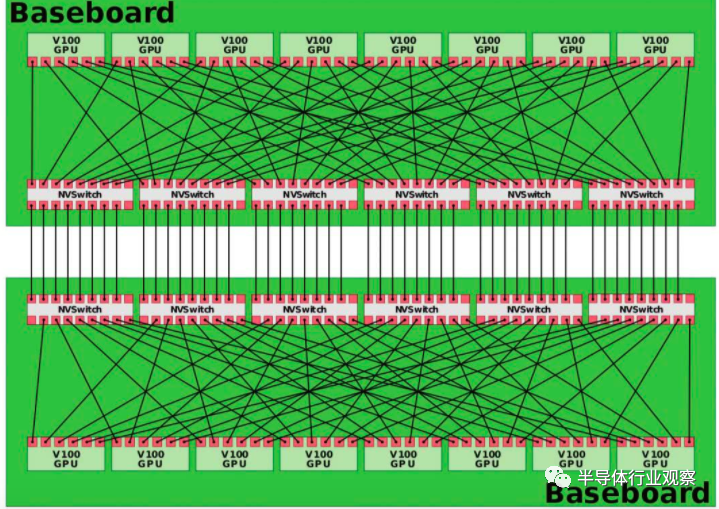

Offload让数据的移动和指令控制分开

那么收购Mellanox和Cumulus的具体用处体现在哪里? 这就要从数据中心的可扩展性(scalability)说起,Nvidia最新发布的DGX A100加速器可以集成8块A100 GPU和2块 AMD的EPYC系列服务器CPU,而单片DGX A100中需要让8块GPU和两块CPU实现两两互联,GPU之间的互联通过Nvidia Link和Nvidia Switch实现,而GPU和CPU的互联通过PCIe- Gen 4实现,复杂的连线使得单片所能容纳的GPU和CPU数量有限,为了能够保证GPU组之间的高效通信用以支持高性能计算工作,这时候就需要实现片间或者服务器之间的高效互联。为此Nvidia通过使用RDMA技术来解决服务器之间的通信问题,所谓RDMA指远程直接数据存取,使得服务器之间可以绕开CPU直接与网卡交换数据,这样,RDMA协议就能够使GPU通过网络,直接读取另外的GPU中的数据,克服了GPU不支持以太网协议栈不能直接处理网卡中数据的弱点,降低了CPU和内存的压力,大大提升了数据中心数据的交换效率。

Nivlink和NivSwitch连接的复杂性

Nvidia此次收购的Mellanox拥有InfiniBand协议产品,是RDMA的网络协议的一种,该协议可以大大提升了数据中心人工智能训练的速度和效率,牢牢占据人工智能相关云端服务器数据互联产品的高地,帮助Nvidia补齐在云数据中心架构方面的短板。

InfiniBand技术大大提升数据中心效率

我们也把InfiniBand这类技术称为SmartNIC(可以理解为智能网卡),其突出强调的两点属性,即通过专用的硬件产品卸载CPU的通信节点功能,并且为普通NIC增加处理器,以方便周边设备通过控制系统总线来直接访问内存。随着软件定义网络(SDN)和网络功能虚拟化(NFV)的发展,SmartNIC也顺应趋势驱动了数据中心虚拟化的发展。

我们看到虽然竞购Mellanox失败,但是作为服务器芯片巨头的Intel并不甘示弱,转手就收购了Barefoot. Barefoot是一家以太网交换机芯片研发公司,自定义了自家的芯片架构PISA,并设计了相应的编程语言P4,直接对标交换机芯片龙头Broadcom,同时Barefoot能为Intel提供数据中心完整的网络功能,驱动数据中心SDN的发展,实现存储、网络和接口的硬件虚拟化,让Intel得到了精细的软硬件资源管理能力,从而更好地为客户提供大型数据中心服务。

四、摩尔定律进入深水区有何影响?

通过前文的描述,我们知道在Dennard Scaling失效后,单纯依靠晶体管尺寸线性缩小来推进摩尔定律变得越来越困难,而且技术的发展也让我们认识到,所有的芯片设计都是在做一个关于PPA的tradeoff的工作,因此在摩尔定律走向深水区以后,便衍生出了关于推进摩尔定律前进的多种路径,比如从晶体管结构、晶体管材料、高功能密度的芯片设计、异构封装和软硬结合多角度来推进其不断前行,而在这其中扮演重要角色的企业涉及到产业链的方方面面,包括芯片设计,芯片制造,芯片封装,网络通信和编程企业等,但万变不离其宗,总结起来,以上方式都是朝着更高计算密度,更大的存储密度和更紧的连接密度三个方向持续推进,最终都是为了实现“单位面积芯片在每瓦每单位成本的基础上实现更高计算能力”这个终极目标,那么在摩尔定律进入深水区以后,会对行业哪些领域未来发展有比较大的影响呢? 笔者认为有以下四个方面。

1、EDA向差异化方向发展

首先,随着芯片设计尤其是加速器设计愈加复杂以及异构封装的崛起,EDA的重要性也越来越凸显,集成电路逻辑仿真、功能验证的工具日益成熟也将设计带入更加复杂的阶段,设计过程和制造和封装过程结合越来越紧密,工程师们通常需要设计出集成CPU / GPU / TPU与一个或多个高带宽内存(HBM)的更加复杂的芯片,这对于EDA的系统级抽象要求更高,设计范畴从芯片扩展到系统,从而提高整个系统设计的一致性,因此无论对于传统的EDA三强还是新兴的创业公司,既是挑战,又是机遇。

其次,目前主流的EDA对x86和Arm架构支持较多,而对RISC-V等架构支持较少,主要是因为目前RISC-V等开源架构生态基础薄弱,与Arm比缺少对GPU和连接技术等IP支持,下游应用较少,目前基本只面向对处理器有定制化需求的客户,且往往只作为协处理器,市场空间有待开发,但是随着客户基于需求多元化、产品安全性和功能复杂性的考虑越来越多,RISC-V灵活多样的定制化能力和扩展性还是可以给很多EDA创业公司带来一个细分领域的市场机会。

第三,异构计算和系统级封装的发展,促使各大公司都会提出自己的芯片架构和封装技术,这时候包含技术标准、规范和协议的IP和工艺重要性日益凸显,EDA可以依靠生态影响力把行业的IP和通用工艺需求固化和领域需求差异化,为专用领域,比如汽车电子,高性能计算等领域提供打包的一揽子解决方案,满足该领域的行业标准及合规性。

第四,新技术的发展促使着EDA的使用方式发生变革,比如人工智能技术开始对EDA产生影响,谷歌研究人员针对芯片设计流程中布局布线阶段提出了一种基于深度强化学习的芯片布局方法,建立了更准确的参数模型,优化参数分析过程。与此同时,EDA走向云端已经初露端倪,并将深刻影响芯片设计流程和模式,降低芯片开发成本,RISC-V架构设计公司SiFive与台积电、微软、Cadence合作,实现了基于云端设计高性能SoC芯片,这也是业界首款采用云计算方式开发出来的芯片。云化服务让EDA公司从按照软件使用收费转为按照服务质量进行收费,但目前云服务的最大阻碍就在于EDA行业的高度垄断,大的EDA公司对此目前只是试水阶段。

2、IP业务将蓬勃发展

不同于EDA行业市场集中度高企,IP业务市场比较分散,各个IP公司都会围绕晶圆制造和客户具体需求做专业化定制,IP业务的发展前景主要体现在:

首先是处理器IP的多元化,包括围绕开源的RISC-V架构和逐渐开放的PowerPC架构和MIPS架构进行IP业务建设,而下游应用端的客户基于产品多样性和安全性角度考虑,需要在x86和Arm两大指令集和芯片架构外定制新的芯片架构,而RISC-V架构、PowerPC架构和MIPS架构可以给芯片设计者和下游应用带来了广泛的选择的机会,降低芯片的设计门槛,给芯片设计带来了发展活力,比如阿里巴巴打造了基于RISC-V的高性能计算芯片玄铁910,同时国内也有睿思芯科、芯来科技和康佳等围绕RISC-V架构开发的IP公司。另外,在加速器方面,针对客户的训练和推理需求不同,专业的IP公司还可以为客户打造针对ISA(指令集)的定制化芯片架构,工具和软件编译器,设计高效的数据访问和处理技术,这方面的代表公司包括以色列的Ceva和台湾的Andes。

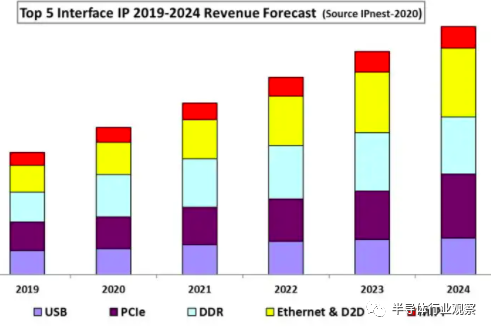

其次,关于I/O连接,存储,以太网PHY解决方案等非处理器IP业务占比将会逐渐提升,在异购计算和系统级封装中,芯片的设计和封装会逐渐专业化和标准化,芯片设计公司可以自行设计芯片架构,同时采购其他公司的高速连接IP,模拟信号IP和存储编译器IP等,组合成SOC或者SIP,整个过程就像“搭积木”一样,实现IP的高可复用,但是无论是向上对接工艺,还是向下对接应用场景,都是一个需要不断调整试错的过程,标准模式不会一成不变,一蹴而就,这方面的代表公司是台湾公司M31和存储技术IP公司Rambus。

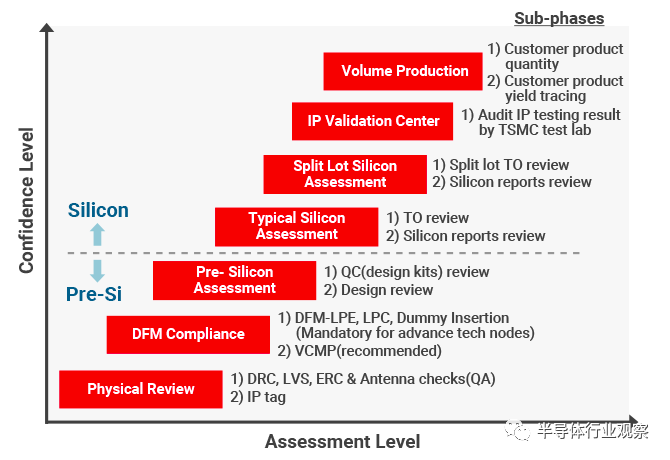

第三,上下游产业结合愈加紧密,IP公司市场份额相对分散化,每家公司专注于自身的细分业务领域,一方面需要向上和制造以及封装工艺配合,另一方面也要紧紧贴合客户需求为客户定制相应IP。台积电作为芯片制造龙头,在整合IP公司方面走在了行业前列,通过吸引IP公司和芯片设计公司与台积电组成开放创新联盟( TSMC Open Innovation Platform),台积电公布相关IP标准,在IP公司提交相关IP方案到台积电的开放平台后,台积电审核过后予以公布,同时Fabless客户也会根据自身采用相关IP方案,并最终由台积电代工,这样可以降低Fabless客户的芯片设计成本(TCO)。

台积电IP平台业务流程

除了打造IP平台以外,台积电还控股了台湾IP公司创意电子(GUC),创意电子主要做CPU和ASIC芯片设计的IP服务,同时深入结合台积电制造和封测业务流程,为客户提供一站式全流程服务;而联电则参股IP公司智原,为客户提供SOC和ASIC芯片设计,也与联电的制造业务密切配合;力积电投资了力旺,力旺则专注于存储领域的IP业务。可以说,芯片制造公司与IP公司密切合作已经成为趋势,IP公司是芯片制造公司对接芯片设计公司的一个窗口。

除此之外,由中芯国际前董事长张汝京创办的芯恩(青岛)集成电路首创了CIDM(Commune IDM)模式,该模式是以产品为导向,以芯片制造公司为主体,基于市场及客户直接的需要,通过联合产业链上下游各方主体,将产业做完整的协同式整合,结合设计、工艺研发、生产制造,为终端客户的需求提供高品质、高效率的产品,相当于一种产业链各方共享资源的共有制IDM公司,这也是产业链上下游紧密合作的代表案例。

除了对接制造和封测等工艺端,一些IP公司还会与下游客户紧密合作,为客户打造基于特定应用的IP产品,比如GPU的IP公司Imagination与北汽合作成立汽车芯片公司,专注于面向ADAS的应用处理器和面向智能座舱的语音交互芯片研发,并从Imagination获得GPU和神经网络加速器(NNA)的IP授权。除此之外, Socionext则开发了针对客户在消费、工业、安防和汽车等不同领域定制化设计成像解决方案的Soc,同时与多家芯片制造厂合作,使得这些制造厂所有的生产能力和公司质量管理体制及设计IP能力形成优势互补。

最后,IP公司其实是半导体行业的服务型公司,我们俗称的“卖水人”,衍生出新的业务模式,除了IP授权(License+Royalty),还包括委托设计(NRE),芯片设计,制造和封装全流程方案(Full Turnkey),驻场服务(FAE)和多客户晶圆验证服务(MPW)等, 从本质上讲就是降低客户芯片设计和制造成本,提高芯片研发效率。随着5G技术发展,衍生出越来越多的垂直领域需求和利基市场,IP公司的服务能力显得尤为必要。

目前全球最大的IP公司主要包括美国的Synopsis、Cadence、SST、Imagination等,笔者认为这些IP公司规模体量大,历史悠久,之前在EDA等领域深耕多年,具有丰富的研发经验和深厚客户基础,但要说最具产业集群模式和参考意义的IP公司,非中国台湾IP公司莫属。

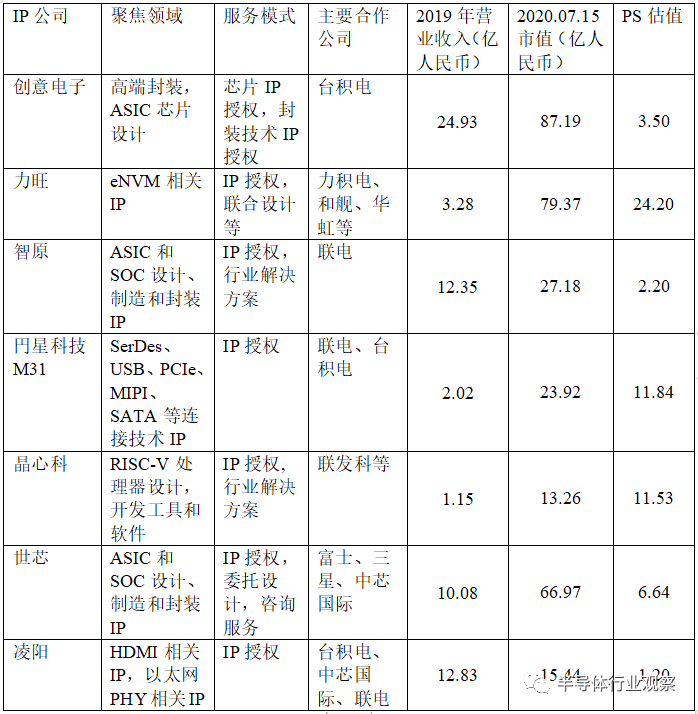

台湾主要IP公司情况

我们看到晶心科,力旺和M31这些前沿的IP服务公司在台湾股市估值很高,表现出市场对新兴处理器和非处理器类的存储以及连接领域IP公司的看好,而根据semiwiki数据,非处理器的IP市场2019年市场规模为8.7亿美元,复合增速为13%,预计到2024年市场规模为16亿美元,增速要高于处理器IP市场4%的复合增速。

非处理器IP市场规模和增速

虽然台湾这两年IP公司蓬勃发展,但我们需要注意的是,台湾IP公司发展是芯片行业发展的自然产物,也是台湾半导体肥沃土壤的结果,摩尔定律进入深水区以后,行业的重心将逐渐转移到制造和封测端,同时行业的分工也会更加细化,半导体制造和封测公司搭建了一个产业平台,吸纳IP公司,尤其是非处理器类业务的IP公司共同发展,建立生态,成为未来行业的一个新方向,而大量优秀的IP公司诞生在台湾这个世界半导体制造高地也就不足为奇了。同时我们对比大陆,虽然有了中芯-长电,青岛芯恩以及广东粤芯等半导体产业链生态的雏形,但是在IP公司多元性以及业务竞争力方面,我们还需要不断加强。

3、先进制造和特殊制造工艺会齐头并进

在台积电,三星,Intel和中芯国际为先进制程你追我赶,突飞猛进时,我们也看到一些制造厂放弃了对于先进制程的追赶,转而专注于成熟制程或者特色工艺,比如Global Foundry、联电和稳懋等。

各大厂制程进度

对先进制程的追赶是摩尔定律不断延伸的直接手段,但是14nm以后的先进制程对资本投入要求非常高,能够追赶先进制程的制造厂目前也只有四家,且目前能够用到先进制程的领域也只有HPC/手机SOC等对计算性能要求高的领域,因而大部分制造厂则专注于成熟制程,利用自身的优势定位于细分行业做差异化竞争。比如专注于Si-Ge工艺的高塔半导体(TowerJazz),是很多光电子芯片设计公司的重要供应商,台湾稳懋专注于GaAs技术代工,三安集成则是大陆领先的专注于GaN、SiC和Vcsel器件的代工企业。可见,宽禁带半导体、GaAs射频、光电子以及Mems等领域,是未来专注于差异化的成熟制程芯片制造厂的选择方向。

4、先进封装业务重要性将得到提升

台积电在半导体封装业务的重视使我们看到封装业务的重要性,从早年依靠先进的FCPOP封装击败三星独享苹果手机芯片制造和封装业务订单,到最近计划投资100亿美元建立先进封装厂,我们都意识到先进封装已经不再是简单的人力密集型行业,而是与制造紧密配合,能够限制提升芯片性能和功耗水平的技术密集型行业。而台积电这样的制造公司做起封装业务,在工艺协调性和成本优化方面,要比单独的OSAT封装公司更具有优势。

先进封装发展趋势

先进封装的发展模糊了半导体产业链的边界,比如在过去电子制造行业形成了晶圆制造、封测和系统组装三个环节,代表厂商分别是台积电、日月光和鸿海,他们的技术精度分别是纳米、微米和毫米级别。随着消费电子产品集成度的提升,部分模组、甚至系统的组装的精度要求逼近微米级别,跟封测环节在工艺上产生了重叠,业务上产生了竞争或协同。

目前先进封装主要用在HPC\手机SOC\消费电子射频等领域,我们拿消费电子来举例,比如高通推出了集成手机AP,天线和射频的方案QSip,这是相对于射频Aip更进一步的先进封装技术,适应了5G技术对于手机高集成度,良好散热和信号损耗尽可能少的要求,预计未来QSip技术会进一步囊括PMIC、Wifi芯片和LPDDR等元器件,使得手机组装和制造更加简洁。同时,无论从Apple Watch的Sip封装还是到Airpods Pro的H芯片Sip封装,我们都能确定先进封装是适应客户需求和产业发展趋势的。

随着先进制程技术程度的提高,产业发展也会出现分化,一类比如大而全的芯片封测公司,如日月光、安靠、长电科技等;一类是专注于CIS等细分领域的封测公司,以自身的差异化取得竞争优势,比如晶方科技,同欣电子,胜丽和精材科技等。

所以笔者认为摩尔定律并没有“死”,芯片技术依然沿着摩尔定律的路径不断进步,只是演绎的方式有所变化。

五、参考文献

1、https://www.eefocus.com/component/461691

2、https://zh.wikipedia.org/wiki/%E6%91

%A9%E5%B0%94%E5%AE%9A%E5%BE%8B

3、https://www.nextplatform.com/2019/

10/23/a-look-inside-the-groq-approach-to-ai-inference/

4、https://www.nextplatform.com/

2020/05/28/diving-deep-into-the-nvidia-ampere-gpu-architecture/

5、http://news.eeworld.com.cn/mp

/ymc/a88744.jspx

6、http://www.semiinsights.com/s/electronic

_components/23/39701.shtml

7、https://www.tsmc.com/english/

dedicatedFoundry/index.htm

8、https://www.hotchips.org/

9、https://www.cerebras.net/

10、https://www.intel.com/content/www/us/en

/products/programmable/intel-agilex-intro.html

11、https://fuse.wikichip.org/news/763/

iedm-2017-sonys-3-layer-stacked-cmos-image-sensor-technology/

12、https://www.mellanox.com/

13、http://news.eeworld.com.cn/mp/Icbank/

a75287.jspx

14、https://new.qq.com/omn/20180709/

20180709A1TLWH.html

15、https://www.amd.com/en

16、https://semiwiki.com/ip/arm/288187

-interface-ip-category-to-overtake-cpu-ip-by-2025/

17、https://v.qq.com/x/page/c09212v402k.html

18、https://spectrum.ieee.org/semiconductors/

processors/the-multiple-lives-of-moores-law

本文为专栏作者授权创业邦发表,版权归原作者所有。文章系作者个人观点,不代表创业邦立场,转载请联系原作者。如有任何疑问,请联系editor@cyzone.cn。

原文链接:https://tech.sina.com.cn/roll/2020-07-21/doc-iivhuipn4195719.shtml